74LS125 Compuerta QUAD Buffer No Inversor de 3 Estados

El 74LS125 es un circuito integrado TTL que contiene cuatro buffers no inversores independientes, cada uno con salida de tres estados (3-State Output).

Gracias a su arquitectura de bajo consumo y alta velocidad, el 74LS125 es ampliamente usado en interfaces digitales, buffers de bus, sistemas de comunicación paralela y controladores TTL. Su encapsulado DIP-14 lo hace ideal para protoboards, placas de desarrollo y montaje en PCB.

Etiquetas :

- Compuertas Logicas ,

- 74LS ,

- BUFFER ,

- DIP

Descripción técnica:

| Especificación | Detalle |

|---|---|

| Familia lógica | TTL – 74LS (Low Power Schottky) |

| Tipo de función | Buffer / Line Driver no inversor |

| Número de buffers | 4 (Quad) |

| Tipo de salida | 3 estados (activo alto) |

| Encapsulado | DIP-14 / PDIP |

| Voltaje de operación (Vcc) | 4.75 V – 5.25 V |

| Nivel lógico alto de entrada (VIH) | Mínimo 2.0 V |

| Nivel lógico bajo de entrada (VIL) | Máximo 0.8 V |

| Nivel lógico alto de salida (VOH) | Mínimo 2.7 V |

| Nivel lógico bajo de salida (VOL) | Máximo 0.4 V |

| Corriente de salida (IOL) | 8 mA (bajo), –0.4 mA (alto) |

| Impedancia de salida (Hi-Z) | Alta, desconectada del bus |

| Tiempo de propagación típico | 14 ns |

| Temperatura de operación | 0 °C a +70 °C |

| Consumo de potencia típico | 2 mW por compuerta |

| Fabricantes equivalentes | Texas Instruments, ON Semiconductor, STMicroelectronics, Fairchild |

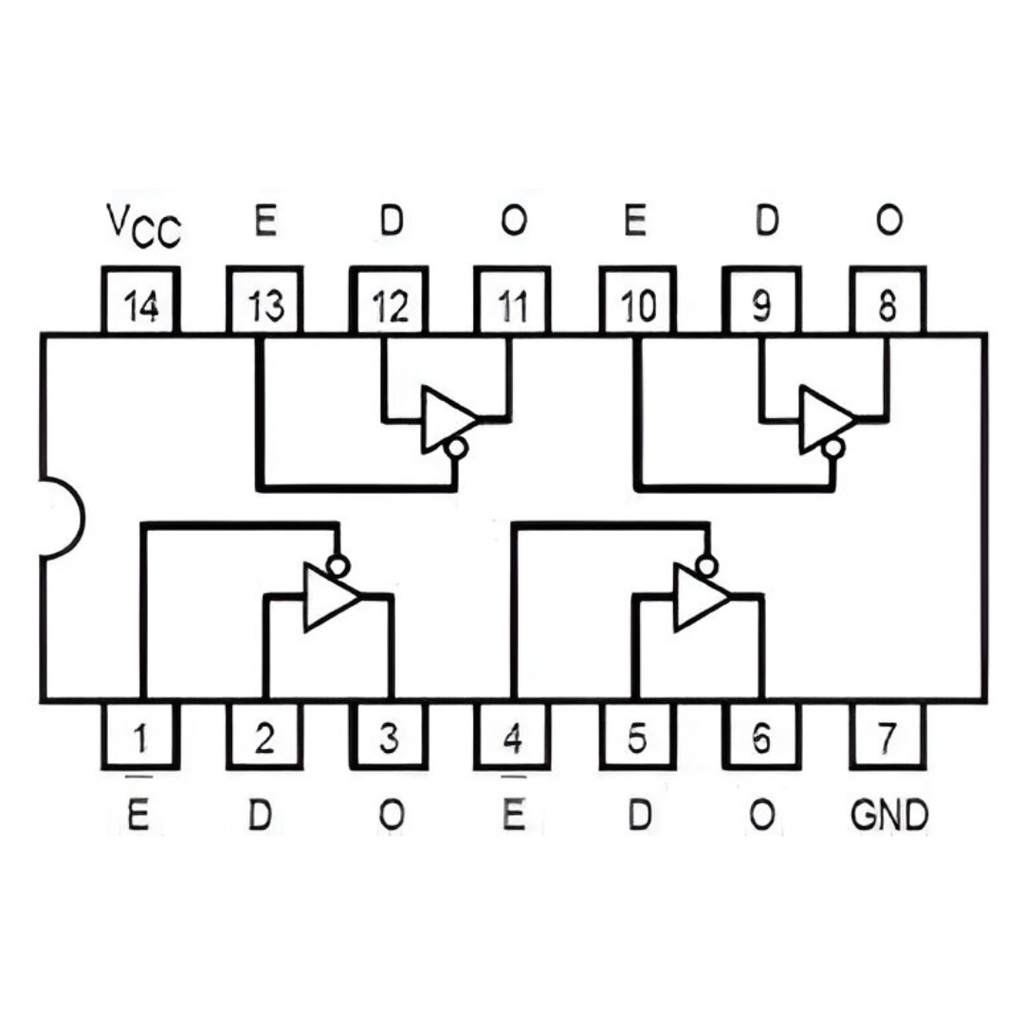

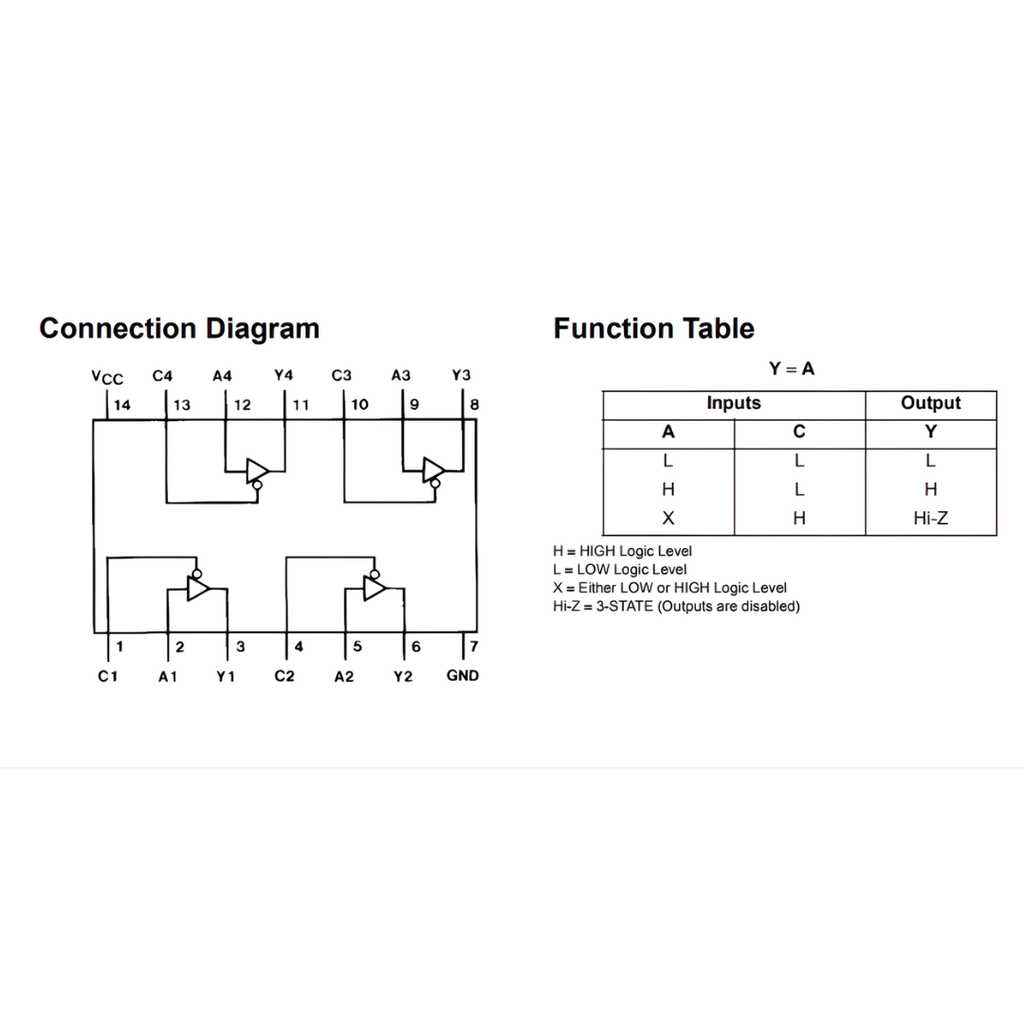

Distribución de pines (DIP-14):

| Pin | Nombre | Descripción |

|---|---|---|

| 1 | 1OE | Habilitación salida 1 (activa baja) |

| 2 | 1A | Entrada buffer 1 |

| 3 | 1Y | Salida buffer 1 |

| 4 | 2OE | Habilitación salida 2 (activa baja) |

| 5 | 2A | Entrada buffer 2 |

| 6 | 2Y | Salida buffer 2 |

| 7 | GND | Tierra |

| 8 | 3Y | Salida buffer 3 |

| 9 | 3A | Entrada buffer 3 |

| 10 | 3OE | Habilitación salida 3 (activa baja) |

| 11 | 4Y | Salida buffer 4 |

| 12 | 4A | Entrada buffer 4 |

| 13 | 4OE | Habilitación salida 4 (activa baja) |

| 14 | Vcc | Alimentación +5 V |

Tabla de funcionamiento lógico

| Entrada (A) | Habilitación (OE) | Salida (Y) |

|---|---|---|

| H | L | H |

| L | L | L |

| X | H | Hi-Z (alta impedancia) |

(H = nivel alto, L = nivel bajo, X = cualquiera, Hi-Z = salida desconectada)

Aplicaciones comunes

- Control y conducción de líneas de bus de datos

- Aislamiento y protección de señales digitales

- Interfases entre microcontroladores y periféricos

- Buffers no inversores para controladores TTL o CMOS

- Multiplexado de señales y control de puertos de E/S