74LS352 Compuerta DUAL Multiplexor de 4 Entradas a 1 Salida Inversa

El 74LS352 es un circuito integrado lógico TTL que contiene dos multiplexores de 4 entradas a 1 salida, con entradas de selección comunes y salidas con compuertas de tres estados. Ideal para aplicaciones de selección de señales digitales, control lógico y procesamiento de datos en proyectos con microcontroladores, Arduino o sistemas TTL.

Etiquetas :

- Compuertas Logicas ,

- 74LS ,

- DIP ,

- Multiplexor

El 74LS352 funciona como un selector digital: permite elegir una de cuatro señales de entrada y enviarla a una salida común.

Este modelo integra dos multiplexores en un solo chip, lo que lo hace muy útil en proyectos donde se requiere optimizar pines de microcontroladores, manejar buses de datos, o diseñar sistemas de control lógicos.

Su tecnología TTL de baja potencia (Low Power Schottky) asegura alta velocidad de conmutación y bajo consumo, características apreciadas en prototipos, equipos educativos, proyectos de robótica o automatización.

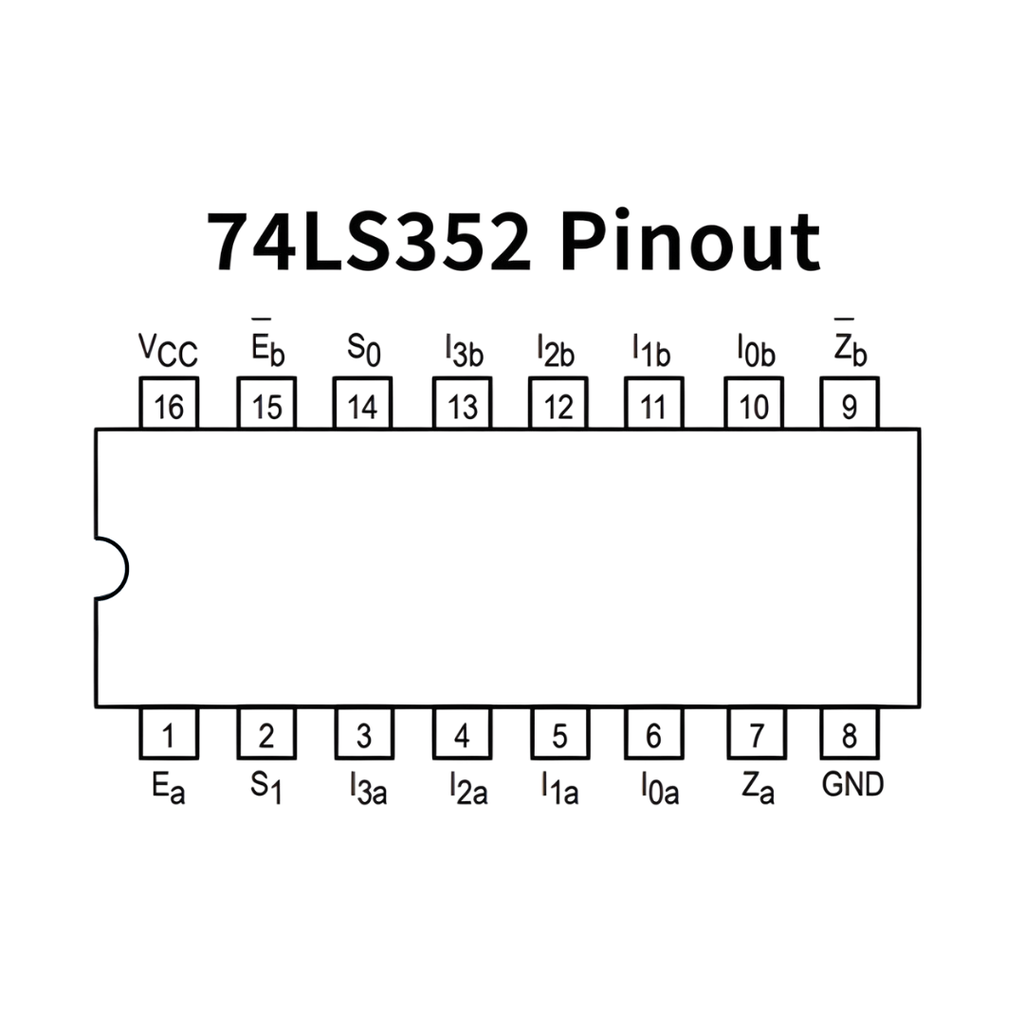

Cada multiplexor tiene 4 entradas de datos, una salida y su propia entrada de habilitación (Enable), pero ambos comparten las líneas de selección (S0 y S1).

Esto significa que el chip puede seleccionar simultáneamente dos bits de datos (A y B), cada uno proveniente de cuatro posibles fuentes, usando las mismas señales de control.

| Parámetro | Descripción |

|---|---|

| Modelo | 74LS352 |

| Tipo de circuito | Dual Multiplexor de 4 canales a 1 salida |

| Familia lógica | TTL LS (Low Power Schottky) |

| Voltaje de operación | 4.75 V a 5.25 V (típico 5 V) |

| Entradas por multiplexor | 4 |

| Salidas | 2 salidas con 3 estados (tri-state) |

| Tiempo de propagación típico | 12 ns |

| Encapsulado | DIP-16 (Dual In-Line Package) |

| Consumo de corriente | Bajo (propio de la familia LS) |

| Temperatura de operación | 0 °C a +70 °C |

| Nº de Pin | Nombre del Pin | Descripción en Español |

|---|---|---|

| 1 | Ea’ | Entrada de habilitación A activa en nivel bajo |

| 2 | S1 | Entrada de selección común 1 |

| 3 | I3a | Entrada del multiplexor A, canal 3 |

| 4 | I2a | Entrada del multiplexor A, canal 2 |

| 5 | I1a | Entrada del multiplexor A, canal 1 |

| 6 | I0a | Entrada del multiplexor A, canal 0 |

| 7 | Za | Salida del multiplexor A |

| 8 | GND | Tierra o referencia de voltaje (0 V) |

| 9 | Zb’ | Salida complementaria del multiplexor B |

| 10 | I0b | Entrada del multiplexor B, canal 0 |

| 11 | I1b | Entrada del multiplexor B, canal 1 |

| 12 | I2b | Entrada del multiplexor B, canal 2 |

| 13 | I3b | Entrada del multiplexor B, canal 3 |

| 14 | S0 | Entrada de selección común 0 |

| 15 | Eb’ | Entrada de habilitación B activa en nivel bajo |

| 16 | Vcc | Voltaje de alimentación del chip (+5 V típico) |